Multiplekser to obwód kombinacyjny, który ma 2Nlinie wejściowe i jedną linię wyjściową. Mówiąc najprościej, multiplekser jest obwodem kombinacyjnym z wieloma wejściami i jednym wyjściem. Informacja binarna odbierana jest z linii wejściowych i kierowana na linię wyjściową. Na podstawie wartości linii wyboru jedno z tych wejść danych zostanie podłączone do wyjścia.

W przeciwieństwie do kodera i dekodera, istnieje n linii wyboru i 2Nlinie wejściowe. Zatem w sumie jest 2Nmożliwe kombinacje wejść. Multiplekser jest również traktowany jako Mux .

Wyróżnia się następujące typy multiplekserów:

Multiplekser 2×1:

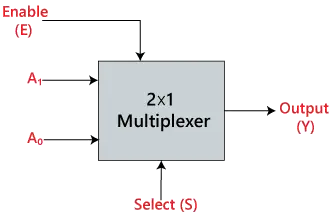

W multiplekserze 2×1 są tylko dwa wejścia, czyli A0i A1, 1 linia wyboru, tj. S0i pojedynczych wyjść, tj. Y. Na podstawie kombinacji wejść występujących na linii wyboru S0, jedno z tych 2 wejść zostanie podłączone do wyjścia. Schemat blokowy i tabela prawdy 2 × Poniżej podano 1 multiplekser.

Schemat blokowy:

Tabela prawdy:

Logiczne wyrażenie terminu Y jest następujące:

T=S0'.A0+S0.A1

Poniżej przedstawiono obwód logiczny powyższego wyrażenia:

Multiplekser 4×1:

W multiplekserze 4×1 znajdują się w sumie cztery wejścia, czyli A0, A1, A2i A3, 2 linie selekcji, tj. S0i S1i jedno wyjście, tj. Y. Na podstawie kombinacji wejść, które są obecne na liniach wyboru S0i S1, jedno z tych 4 wejść jest podłączone do wyjścia. Schemat blokowy i tabela prawdy 4 × Poniżej podano 1 multiplekser.

Schemat blokowy:

Tabela prawdy:

Logiczne wyrażenie terminu Y jest następujące:

T=S1' S0' A0+S1' S0A1+S1S0' A2+S1S0A3

Poniżej przedstawiono obwód logiczny powyższego wyrażenia:

Multiplekser 8 do 1

W multiplekserze 8 do 1 dostępnych jest łącznie osiem wejść, tj. A0, A1, A2, A3, A4, A5, A6i A7, 3 linie selekcji, tj. S0, S1i S2i jedno wyjście, tj. Y. Na podstawie kombinacji wejść, które są obecne na liniach wyboru S0, S1,i S2, jedno z tych 8 wejść jest podłączone do wyjścia. Schemat blokowy i tabela prawdy 8 × Poniżej podano 1 multiplekser.

Schemat blokowy:

Tabela prawdy:

Logiczne wyrażenie terminu Y jest następujące:

T=S0'.S1'.S2'.A0+S0.S1'.S2'.A1+S0'.S1.S2'.A2+S0.S1.S2'.A3+S0'.S1'.S2A4+S0.S1'.S2A5+S0'.S1.S2.A6+S0.S1.S3.A7

Poniżej przedstawiono obwód logiczny powyższego wyrażenia:

Multiplekser 8 × 1 wykorzystujący multiplekser 4 × 1 i 2 × 1

Możemy wdrożyć 8 × 1 multiplekser wykorzystujący multiplekser niższego rzędu. Aby wdrożyć 8 × 1 multiplekser, potrzebujemy dwóch 4 × 1 multipleksery i jeden 2 × 1 multiplekser. 4 × 1 multiplekser ma 2 linie wyboru, 4 wejścia i 1 wyjście. 2 × 1 multiplekser ma tylko 1 linię wyboru.

Aby uzyskać 8 wejść danych, potrzebujemy dwóch 4 × 1 multipleksery. 4 × 1 multiplekser wytwarza jedno wyjście. Aby uzyskać ostateczny wynik, potrzebujemy 2 × 1 multiplekser. Schemat blokowy 8 × 1 multiplekser wykorzystujący 4 × 1 i 2 × Poniżej podano 1 multiplekser.

Multiplekser 16 do 1

W multiplekserze 16 do 1 jest łącznie 16 wejść, tj. A0, A1, …, A16, 4 linie selekcji, tj. S0, S1, S2i S3i jedno wyjście, tj. Y. Na podstawie kombinacji wejść, które są obecne na liniach wyboru S0, S1i S2, jedno z tych 16 wejść zostanie podłączone do wyjścia. Schemat blokowy i tablica prawdy 16 × 1

Schemat blokowy:

Tabela prawdy:

Logiczne wyrażenie terminu Y jest następujące:

T=A0.S0'.S1'.S2'.S3'+A1.S0'.S1'.S2'.S3+A2.S0'.S1'.S2.S3'+A3.S0'.S1'.S2.S3+A4.S0'.S1.S2'.S3'+A5.S0'.S1.S2'.S3+A6.S1.S2.S3'+A7.S0'.S1.S2.S3+A8.S0.S1'.S2'.S3'+A9.S0.S1'.S2'.S3+Y10.S0.S1'.S2.S3'+A11.S0.S1'.S2.S3+A12 S0.S1.S2'.S3'+A13.S0.S1.S2'.S3+A14.S0.S1.S2.S3'+A15.S0.S1.S2'.S3Poniżej przedstawiono obwód logiczny powyższego wyrażenia:

Multiplekser 16×1 wykorzystujący multiplekser 8×1 i 2×1

Możemy wdrożyć 16 × 1 multiplekser wykorzystujący multiplekser niższego rzędu. Aby wdrożyć 8 × 1 multiplekser, potrzebujemy dwóch 8 × 1 multipleksery i jeden 2 × 1 multiplekser. 8 × 1 multiplekser ma 3 linie wyboru, 4 wejścia i 1 wyjście. 2 × 1 multiplekser ma tylko 1 linię wyboru.

Aby uzyskać 16 wejść danych, potrzebujemy dwóch multiplekserów 8 × 1. 8 × 1 multiplekser wytwarza jedno wyjście. Aby uzyskać ostateczny wynik, potrzebujemy 2 × 1 multiplekser. Schemat blokowy 16 × 1 multiplekser wykorzystujący 8 × 1 i 2 × Poniżej podano 1 multiplekser.