Flip-flop to termin należący do elektroniki cyfrowej i jest to element elektroniczny używany do przechowywania jednego bitu informacji.

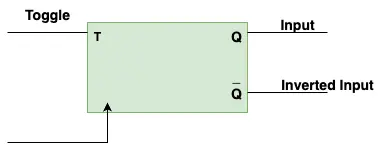

Schematyczne przedstawienie przerzutnika

- Ponieważ Flip Flop jest obwodem sekwencyjnym, jego wejście opiera się na dwóch parametrach, jeden to wejście prądowe, a drugi to wyjście z poprzedniego stanu.

- Ma dwa wyjścia, oba są uzupełnieniem siebie.

- Może znajdować się w jednym z dwóch stabilnych stanów: 0 lub 1.

Podstawowy schemat flip flopa

Co to jest T Flip Flop?

- T flip flop, a dokładniej, jest znany jako Toggle Flip Flop, ponieważ może przełączać wyjście w zależności od wejścia.

- T tutaj oznacza Przełącznik .

- Przełącznik zasadniczo wskazuje, że bit zostanie odwrócony, tj. Z 1 na 0 lub z 0 na 1.

- Tutaj dostarczany jest impuls zegarowy do obsługi tego przerzutnika, dlatego jest to przerzutnik taktowany.

Budowa T Flip Flopa

Możemy skonstruować T flip na trzy sposoby, a mianowicie:

- Używając klapek SR.

- Za pomocą klapek D.

- Używając klapek JK

Sposoby konstrukcji T Flip Flop

Zobaczmy konstrukcję T Flip Flop przy użyciu przerzutników SR, które wymagają 2 bramek AND i 2 bramek NOR, jak pokazano poniżej:

Podstawowy schemat blokowy T Flip Flop

Tutaj schemat blokowy zawiera wejścia przełączające i zegarowe, Q i Q’ to uzupełnione wejścia.

Działanie T Flip Flopa

Przypadek 1 : Powiedzmy, T = 0 i puls zegarowy wysoki tj. 1, wówczas wyjście obu bramek AND 1 i bramki 2 będzie 0 , brama 3 wyjście będzie Q i podobnie brama 4 wyjście będzie Q' więc obie wartości Q i Q’ są takie same jak ich poprzednia wartość, co oznacza Utrzymaj stan .

Przypadek 2 : Powiedzmy, T=1 , wówczas wyjście obu bramek AND 1 będzie (T * zegar * Q) , a ponieważ T i zegar wynoszą 1, wówczas wyjście bramki AND 1 będzie takie Q , i podobnie będzie wyjście bramki AND 2 (T * zegar * Q’) tj., Q' . Teraz wyjście bramki 3 będzie (Q’+Q)’ i powiedzmy, że Q’ wynosi zero, wtedy wyjście bramki 3 będzie takie (0+Q)’ co znaczy Q' i podobnie będzie wyjście bramki 4 (P+P’)’ a ponieważ Q’ wynosi zero, zatem wyjście bramki 4 będzie miało wartość Q’, co oznacza 0 ponieważ Q’ wynosi zero. Dlatego w tym przypadku możemy powiedzieć, że wyjście jest przełączane, ponieważ T=1 .

Tabela prawdy T Flip Flop

- Tutaj T jest wejściem przełączającym, Q jest wejściem stanu obecnego, Qt+1 jest wyjściem następnego stanu.

- Stąd widzimy, że ilekroć wartość Toggle (T) wynosi 0, wyjście następnego stanu (Qt+1) jest takie samo, jak wejście stanu bieżącego (Q).

- Ilekroć Toggle (T) ma wartość 1, wyjście następnego stanu (Qt+1) będzie uzupełnieniem wejścia stanu bieżącego (Q), co oznacza, że zostanie przełączone.

Równanie charakterystyczne

- Równanie charakterystyczne mówi nam o tym, jaki będzie następny stan przerzutnika w odniesieniu do stanu obecnego.

- Aby uzyskać równanie charakterystyczne, konstruowana jest K-Map, która zostanie pokazana poniżej:

- Jeśli rozwiążemy powyższą mapę K, wówczas otrzymamy równanie charakterystyczne Q(n+1) = TQn’ + T’Qn = T XOR Qn

Tabela wzbudzeń

Tabela wzbudzeń zasadniczo mówi o wzbudzeniu wymaganym przez przerzutnik, aby przejść z bieżącego stanu do następnego stanu.

- Tutaj, ilekroć T wynosi 0, Qt+1 jest takie samo jak wejście Q.

- I ilekroć T wynosi 1, Qt+1 jest uzupełnieniem wejścia Q.

Zastosowania T Flip Flop

Istnieje wiele zastosowań T Flip Flop w systemie cyfrowym, które są wymienione poniżej:

- Liczniki : T Klapki używane w licznikach. Liczniki zliczają liczbę zdarzeń występujących w systemie cyfrowym.

- Przechowywanie danych : T Przerzutniki używane do tworzenia pamięci używanej do przechowywania danych po wyłączeniu zasilania.

- Synchroniczne obwody logiczne : Przerzutniki T można wykorzystać do realizacji synchronicznych obwodów logicznych, czyli obwodów wykonujących operacje na danych binarnych w oparciu o sygnał zegarowy. Synchronizując działanie obwodu logicznego z sygnałem zegarowym za pomocą przerzutników typu T, zachowanie obwodu może być przewidywalne i niezawodne.

- Podział częstotliwości : Służy do dzielenia częstotliwości sygnału zegara przez 2. Przerzutnik przełącza wyjście za każdym razem, gdy sygnał zegara przechodzi z wysokiego na niski lub z niskiego na wysoki, dzieląc w ten sposób częstotliwość zegara przez 2.

- Rejestry przesuwne : Przerzutniki T mogą być używane w rejestrach przesuwnych, które służą do przesuwania danych binarnych w jednym kierunku.

Wniosek

W tym artykule zaczynamy od podstaw przerzutników, czyli tego, czym właściwie są przerzutniki, a następnie omówiliśmy przerzutniki T, trzy dwa sposoby konstruowania przerzutników T, jest to podstawowy diagram blokowy, działanie przerzutnika T , to tabela prawdy, równanie charakterystyczne oraz tabela wzbudzeń, a na koniec omówiliśmy zastosowania przerzutników T.